HSD LVDS Automotive High Frequency Connectors Hsd Lvds Automotive High Frequency Connectors,Automotive High Frequency Connectors,12Pin Male Connecor For Cable,High Speed Connector For Cable Dongguan Zhuoyuexin Automotive Electronics Co.,Ltd , https://www.zyx-fakra.com

The biggest challenge for developers is the lack of clear separation between core and non-core domains, which often leads to writing non-reusable code that doesn't contribute to the product's competitive advantage. This includes areas like requirements, algorithms, user experience, and software engineering practices. As a result, more time and resources are spent on maintenance than on initial development.

Teams that create great products not only have stable workforces but also enjoy higher income and a different mindset. They use effective development strategies and quickly master technologies that outperform traditional "old programmers." While many companies offer high salaries, the products developed by others succeed in the market, while yours may not. This waste of investment leads to missed opportunities for creating greater value.

More than a decade ago, the author faced similar challenges and decided to focus on developing standardized platform technology for software and hardware. This led to the creation of AWorks. Ametal, derived from the Aworks-Nano subset, supports cross-platform functionality and defines standard interfaces for peripheral devices, enabling "on-demand" services. It has become a reality.

ZLG provides users with numerous standard peripheral drivers and protocol components, aiming to build a complete ecosystem. No matter which MCU you choose, as long as it supports AMetal, you can achieve "one-time programming, lifelong use," eliminating the need to reinvent the wheel.

**6.1 E2PROM Memory**

E2PROM (Electrically Erasable Programmable Read-Only Memory) is a type of memory that retains data even after power loss. This section uses FM24C02 as an example to explain how to use similar non-volatile memory in AMetal.

> > >

**6.1.1 Device Introduction**

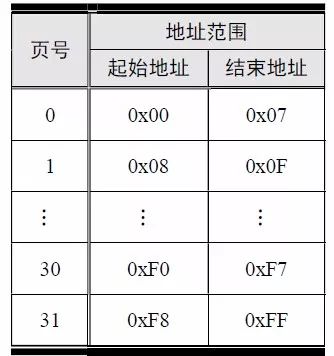

The FM24C02 has a total capacity of 2K bits (256 bytes). Each byte corresponds to a unique address, ranging from 0x00 to 0xFF. The page size is 8 bytes, and writes cannot cross page boundaries. For example, addresses like 0x08, 0x10, 0x18 must be written separately if the data crosses a boundary. The memory structure is shown in Table 6.1.

Table 6.1: FM24C02 Memory Organization Structure

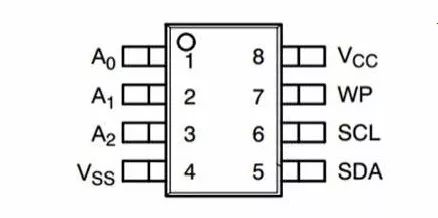

The communication interface of the FM24C02 is a standard I²C interface, using SDA and SCL lines. For example, in an 8-pin SOIC package, the WP pin is used for write protection. When tied high, it blocks all write operations; otherwise, it is grounded for normal access.

Figure 6.1: FM24C02 Pin Definition

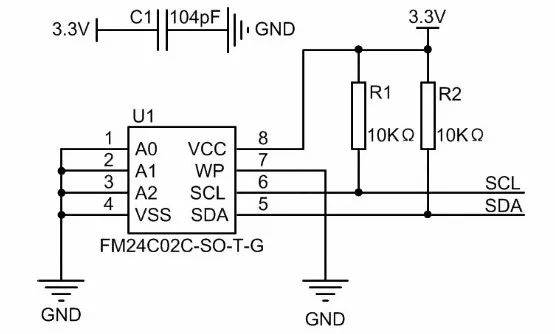

A2, A1, and A0 determine the I²C slave address, which is 0x50 when all are grounded. In AMetal, the address is represented as a 7-bit address. The MicroPort-EEPROM module connects to the AM824-Core via the MicroPort interface.

Figure 6.2: E2PROM Circuit Schematic

> > >

**6.1.2 Initialization**

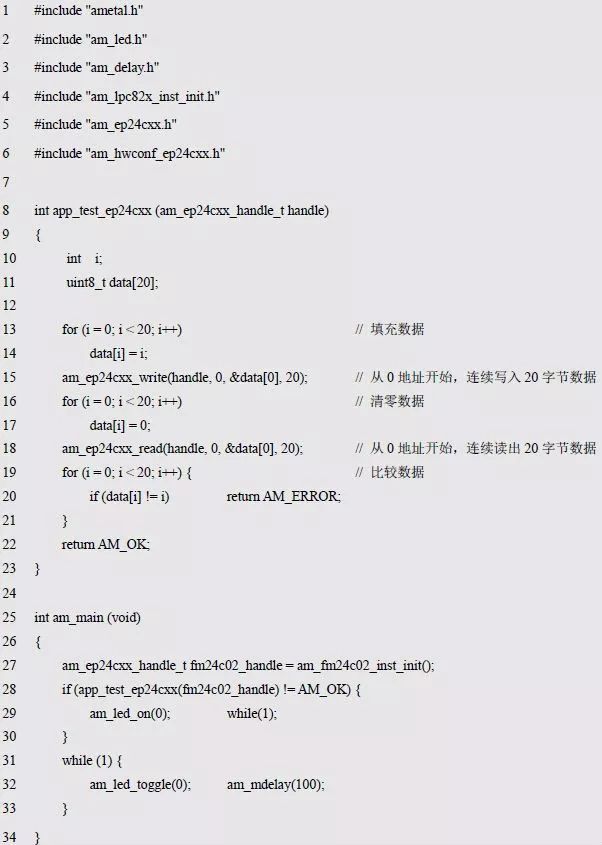

AMetal provides driver functions for I²C interface E2PROMs like FM24C02, FM24C04, and FM24C08. An example function prototype is:

This function returns a device instance handle, where `p_dev` is a pointer to an `am_ep24cxx_dev_t` instance, and `p_devinfo` is a pointer to `am_ep24cxx_devinfo_t`.

**Instance**

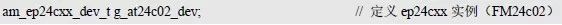

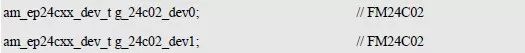

An FM24C02 is an instance of EP24Cxx. If one FM24C02 is connected to the I²C bus, the instance is defined as follows:

If two FM24C02s are connected, three instances are needed:

Each instance is initialized and returns a handle for later operations.

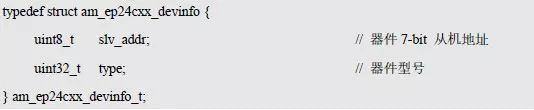

**2. Instance Information**

The instance information defines the specific device, such as its I²C slave address and model. For FM24C02, the macro `AM_EP24CXX_FM24C02` is used.

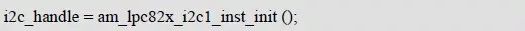

**3. I²C Handle `i2c_handle`**

Taking I²C1 as an example, the return value of `am_lpc82x_i2c1_inst_init()` is passed as `i2c_handle`.

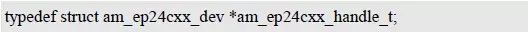

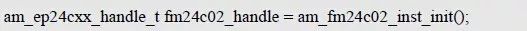

**4. Example Handle `fm24c02_handle`**

The initialization function `am_ep24cxx_init()` returns `fm24c02_handle`, which is used for read/write operations.

If the return value is NULL, initialization failed; otherwise, a valid handle is returned.

Based on modular programming, the instance and configuration are stored in the corresponding files, and the header file provides the interface.

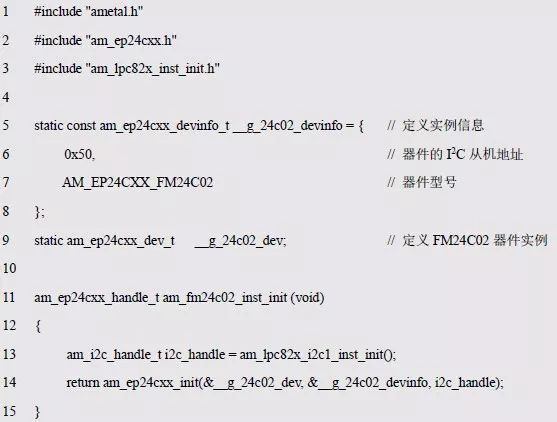

**Listing 6.1 Example Initialization Function (am_hwconf_ep24cxx.c)**

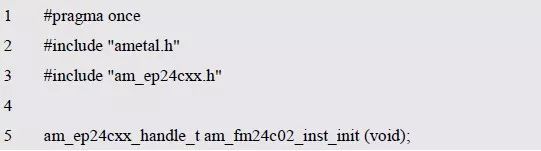

**Listing 6.2 Interface Declaration (am_hwconf_ep24cxx.h)**

Subsequent calls use the parameterless function to get the handle.

Note: `i2c_handle` distinguishes I²C0, I²C1, etc., while the instance handle distinguishes multiple devices on the same system.

> > >

**6.1.3 Read and Write Functions**

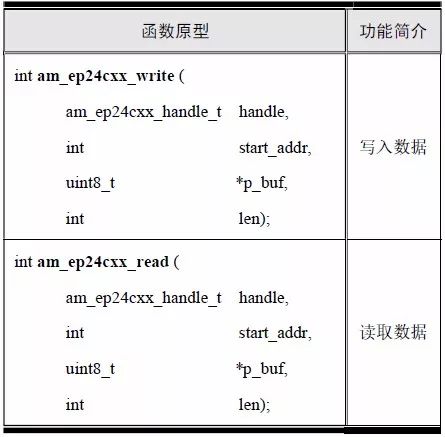

The function prototypes for reading and writing EP24Cxx series memory are shown in Table 6.2.

Table 6.2: EP24Cxx Read and Write Functions (am_ep24cxx.h)

Return values: `AM_OK` means success, negative values indicate failure. Positive values are API-specific.

**1. Data Writing**

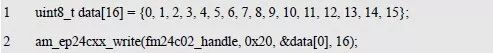

The function prototype for writing data starting at a specified address is:

Assume writing 16 bytes from 0x20:

**2. Data Reading**

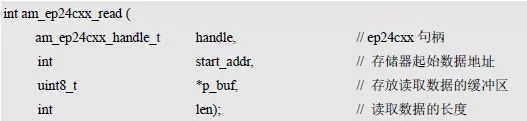

The function prototype for reading data starting at a specified address is:

Assume reading 16 bytes from 0x20:

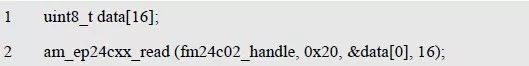

As shown in Listing 6.5, write 20 bytes and compare the read results.

Since `app_test_ep24cxx()` depends on the EP24Cxx device, it cannot be used across platforms.

> > >

**6.1.4 NVRAM Universal Interface Functions**

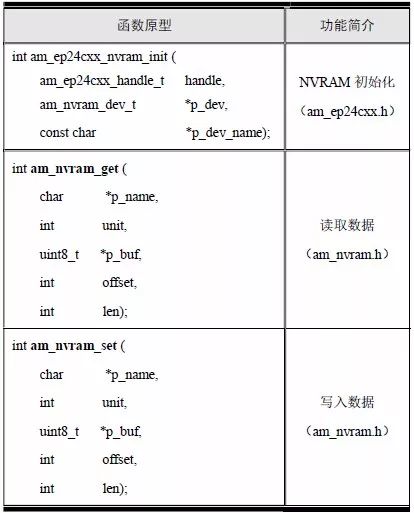

Using the NVRAM (Non-Volatile RAM) standard interface for E2PROM like FM24C02 eliminates the need to care about specific devices. Before using these functions, set `AM_CFG_NVRAM_ENABLE` to 1 in `am_prj_config.h`. The function prototypes are shown in Table 6.3.

Table 6.3: NVRAM Common Interface Functions

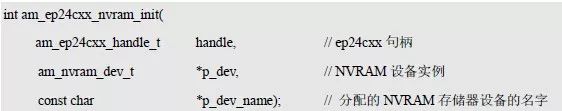

**1. Initialization Function**

The NVRAM initialization function sets up the interface for reading and writing. Its prototype is:

The `fm24c02_handle` is passed as the `handle`, `p_dev` points to an `am_nvram_dev_t` instance, and `p_dev_name` is the name assigned to the FM24C02 for identification.

**(1) Example (NVRAM Memory)**

NVRAM represents all non-volatile memory. Define an `am_nvram_dev_t` instance:

**(2) Instance Information**

The instance information contains the device name, such as `"fm24c02"`. Multiple devices can be named `"fm24c02_0"`, `"fm24c02_1"`, etc.

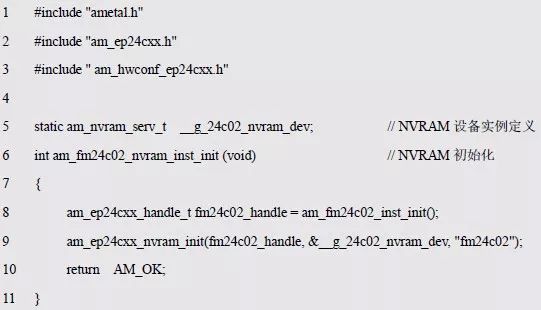

Based on modular programming, the code is stored in the configuration file, and the interface is extracted through the header file.

**Listing 6.6 NVRAM Instance Initialization (am_hwconf_ep24cxx.c)**

**Listing 6.7 am_hwconf_ep24cxx.h File Update**

Afterward, call the parameterless function to initialize the NVRAM device named `"fm24c02"`:

**2. Storage Segment Definition**

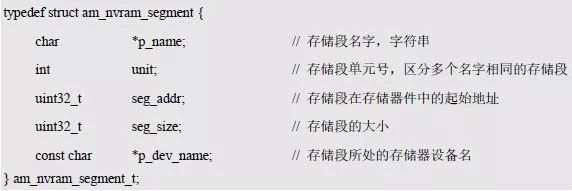

NVRAM defines storage segments, each identified by a name and unit number. The type `am_nvram_segment_t` is defined as:

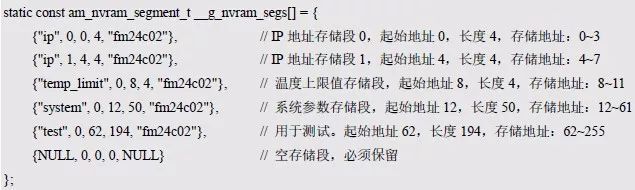

Segments are defined in `am_nvram_cfg.c`. For example, define 5 segments for storing IP addresses, temperature limits, and system parameters:

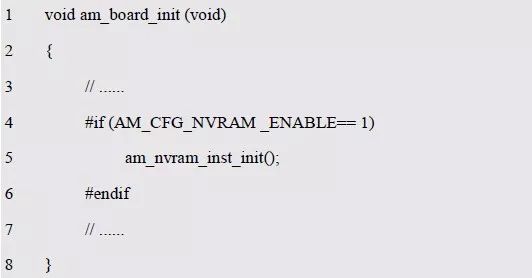

Call `am_nvram_inst_init()` during system startup to load the segments.

**Listing 6.8 Board-Level NVRAM Initialization**

After initialization, 5 segments are available for reading and writing.

**Table 6.4 NVRAM Buckets**

**3. Data Writing**

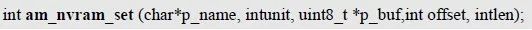

The write function prototype is:

For example, saving an IP address to an IP bucket:

**4. Data Reading**

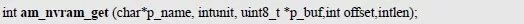

The read function prototype is:

For example, reading an IP address from the IP bucket:

Finally, test the NVRAM interface with a simple program.

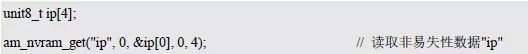

**Listing 6.11 Test Program Implementation (app_test_nvram.c)**

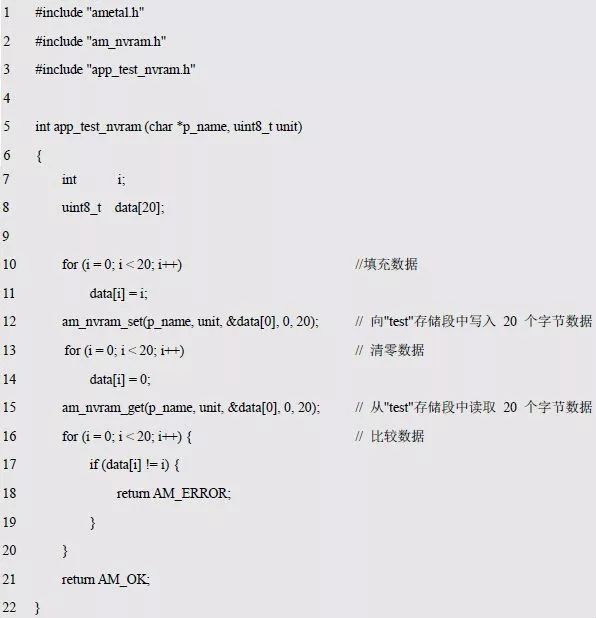

**Listing 6.12 Interface Declaration (app_test_nvram.h)**

The segment to test is passed as a parameter, and the NVRAM interface reads and writes to it. If the data matches, return `AM_OK`; otherwise, return `AM_ERROR`.

The application does not contain any device-specific code, relying solely on the NVRAM interface for cross-platform compatibility.

**Listing 6.13 NVRAM Universal Interface Read and Write Sample**

The NVRAM interface improves readability and maintainability by using named segments. However, it consumes more memory and CPU resources, so the EP24Cxx interface is recommended for high-performance or memory-constrained applications.

September 05, 2025