With the increasing complexity of SoC and SIP in the mass consumer industry, the contradiction between the two basic requirements of low cost and high device life cycle has become more prominent. Consumers demand improved performance on the basis of the same or lower cost, and they often propose new improvements. Therefore, components must be thoroughly tested at low cost and extremely quickly. While greatly reducing the throughput overhead of the ATE architecture, it can provide more parallel processing capabilities in the test, which may properly solve the additional time problems caused by the increasingly complex test devices. In order to solve the emerging analog core problems in leading-edge consumer devices, in addition to the above two measures, the resolution and accuracy of the ATE hardware must also be guaranteed. The simple 10-bit effective resolution and 4KHz bandwidth can meet the audio quality requirements of early wireless phones. The latest development trends show that the device can support more stringent CD quality audio performance, stereo and surround sound specifications. The market claims to have 24-bit audio resolution, and the actual effective performance is generally 16 to 17 bits, which is equivalent to a dynamic range of 98dB to 104dB, and a bandwidth of 20KHz.

We make 7.4v 2000mah to 20Ah Li Ion Battery Pack for heated clothing all types, including heated glove, heated jacket, heated coat, heated vest, heated shirt, electric heated jacket, heated pants, heated boots, heated gloves, heated underwear, heated jacket liners, heated glove liners, heated work glove, heating vest, heating clothing, heated motorcycle jacket, heated hunting jacket.

most popular model is 7.4v 2 cells battery, typical capacity 2200-2400mah, 2500-2600mah, 2900-3000mah, 3200-3400mah.

7V Heated Glove Battery,Heated Gloves Battery,Hand Warmers Battery,Warmest Gloves Battery Asarke Industry Co., Limited , https://www.asarke-industry.com

Audio DAC and ADC

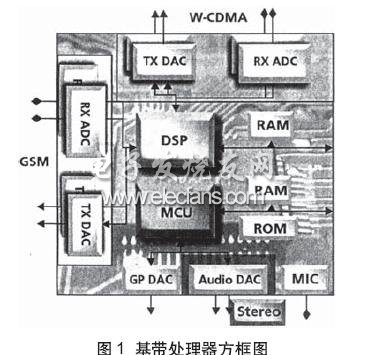

The highly integrated SoC device, as shown in the wireless mobile phone baseband processor shown in Fig. 1, has built-in multiple functional blocks with different performances, withstanding the double pressure of specification and test time.

When the consumer uses discrete CD-quality DACs and ADCs, ATE-related test costs can still be met due to the initiative to increase device prices. When integrating CD-quality cores in SoCs, additional functions increase test time and negative impact on test cost (COT). Increasing device prices can no longer compensate for the increase in ATE test costs.

Audio core test time derivation example

For dynamic testing of mixed signals, it is essential to prevent the leakage of the spectrum generated in the analysis process. Therefore, the following relationship must be satisfied:

M / N = Ft / Fs

In the formula, M is the number of capture cycles; N is the number of sampling points; Ft is the test signal frequency; Fs is the sampling frequency.

For low-fidelity audio devices, such as microphones input by ADC or headphones output by DAC, 8KHz sampling frequency is adopted, which is equivalent to 4KHz bandwidth. If the test signal frequency is 1.03125KHz, 66 cycles can be captured relative to the 8KHz sampling frequency and 512 point acquisition. The sampling time is equal to the number of sampling points divided by the sampling frequency, which is 64ms. Audio test requires more than 10 tests, including multiple gain states; idle channel noise (ICN), crosstalk (XTALK) and intermodulation distortion (IMD), so that even for a simple core, the total test time is also It takes 650ms.

From the ATE analog or digital capture memory to transfer 20-bit sampling data to the workstation, the test overhead is also very considerable. In order to determine the amount of data transfer for analysis, 20 bits are multiplied by the number of sampling points N, and then multiplied by the number of times the core is tested. In this example, 20 digits & TImes; 512 points & TImes; 10 measurements, a total of 102,400 digits. Assuming that the bandwidth between the analog module and the workstation is 1MB, the transmission time of the test DAC core is about 100ms. The transfer overhead of the digital capture memory is also 100ms under the same bandwidth. Therefore, for voice quality DAC and ADC testing, the 200ms transmission overhead increases the total test time to 1500ms (650ms + 650ms + 200ms).

Parallel test overhead of ATE architecture

To further illustrate this issue, consider the impact of surround sound audio processors on test time. AC3 digital audio provides 6 analog outputs: front L / R; surround sound L / R; center speaker and ultra-low single speaker. From an analog perspective, these devices require a combination of high dynamic range and parallel testing.

CD quality dynamic range and bandwidth require a higher sampling rate. Using the above formula and replacing it with Fs = 4.8KHz, the sampling time is 10.7ms. Taking into account hardware settings, test stability and other overhead, the test time is 15ms. Taking into account more than 10 measurement times, the total test time rose to 150ms. In this way, for each channel of 6 channels, the serial test implementation will take 900ms.

The test point implementation scheme can take full advantage of the parallel testing of multiple waveform digitizers. However, data transmission is still serial in the multi-test point test, and the transmission overhead is accumulated. Therefore, even with 4 waveform digitizers, the 4 test point test implementation requires 900ms + 4 & TImes; 600ms = 3300ms.

Multi-standard wireless baseband processor

Wireless devices set multiple standards in the same phone. To support these standards, chipsets often have redundant baseband analog converters and RF transceivers. As in the audio surround sound processor, many analog cores in the wireless baseband processor have a huge impact on the test time. The main problem in testing these devices is how to set up sufficient parallel tests in the simulation test hardware to obtain the efficiency of multiple test points.

The baseband processor block is composed of quadrature (I / O) transmit (TX) DAC and receive (RX) ADC pairs. In 2G to 2.75G GSM / GPRS / EDGE technology, the carrier channel spacing is limited to 200KHz, resulting in low frequency zero IF. W-CDMA uses a 5MHz channel and the corresponding bandwidth is wider.

The RX and TX paths usually require full dynamic testing, including signal pair distortion (SND), CIN, and XTALK. I / Q also requires gain matching and phase matching tests for DAC and ADC. The specifications are specified within 0.1dB and 3 degrees of high accuracy. The requirement to ensure channel isolation during transmission results in additional out-of-band (00B) attenuation testing of the DAC. Adjacent channel power ratio (ACPR) can confirm the degree of channel isolation. For W-CDMA with DAC, the OOB frequency is up to 10MHz.

High-definition video encoder

Current SoC devices support multiple video input standards. Traditional NTSC or PAL devices are equipped with super video CS-VIDEO and composite analog output. Supporting HDTV requires 3 additional outputs to provide a signal that conforms to YPrPbHDTV (EIA-770.1-3). To prepare all the above outputs, 6 video DACs are required: 2 for S-Video, 1 for composite output, and 3 for RGB.

Although the highest required interface speed of the digital video standard is 74MHz, the analog bandwidth required to test the performance of the DAC is about 8MHz with a resolution of 10 to 12 bits. Typical test items for a single video DAC include integral nonlinearity (INL), differential nonlinearity (DNL), and SND measurement. The graphics quality of the HDTV system is determined by the relative accuracy of the DAC output, and additional tests must be performed on the output gain and phase matching. The total test time of the built-in digital video device is directly related to the number of parallel digitizers available for testing. The number of video DACs to be tested is usually more than six. Due to the lack of tester resources, it is essential to establish a serialized test solution.

June 19, 2020