PWM buzzer driven FPGA online download configuration diagram

Begin by connecting the USB Blaster download cable to your computer and the SF-CY4 board. Power on the SF-CY4 board, then open the project located in the "...\prj\cy4ex2" directory by double-clicking the "cy4.qpf" file. As shown in Figure 7.18, click the "Programmer" button in the menu bar to access the download configuration settings.

Figure 7.18: Programmer Button

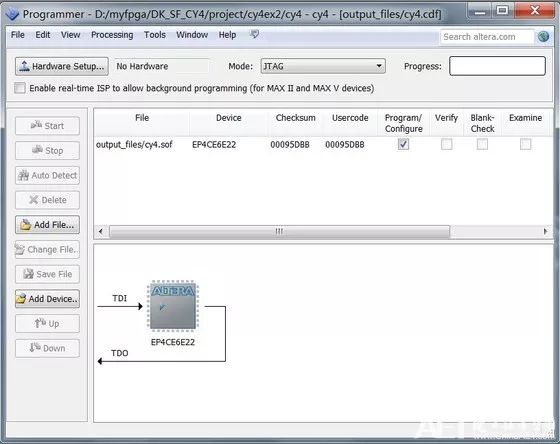

Once you are on the Programmer page (as shown in Figure 7.19), make sure that the "Mode" is set to "JTAG". Verify that the file listed under the "File" column is "output_files/cy4.sof", and check the box labeled "Program/Configure". This ensures that the correct file will be programmed into the FPGA.

Figure 7.19: Programmer Page

Next, confirm that Quartus II recognizes the USB Blaster. If it does not appear, click on "Hardware Setup..." located at the top left of the screen, as shown in Figure 7.19.

In the Hardware Setup window (Figure 7.20), select "USB Blaster" from the list of available hardware devices. Then close the dialog box. If the USB Blaster option is not visible, ensure that the USB Blaster is properly connected to both the PC and the SF-CY4 board. Try unplugging and reinserting the USB cable several times, or restart the Quartus II software if necessary.

Figure 7.20: Downloader Identification and Selection

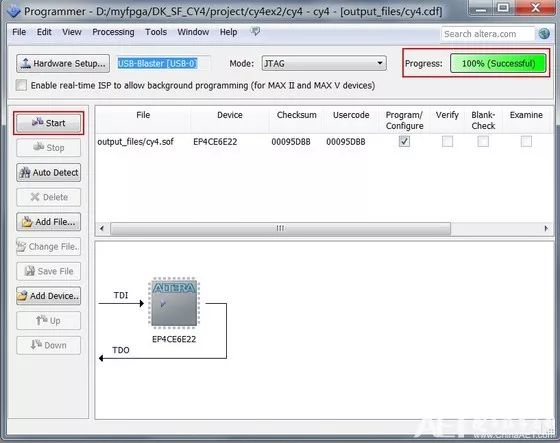

After confirming all settings, as shown in Figure 7.21, click the "Start" button on the right side of the screen to begin the programming process. Observe the progress bar in the upper-left corner, which should move from 0% to 100%. Upon completion, you may hear a short "drip" sound from the buzzer on the SF-CY4 development board, indicating a successful download.

Figure 7.21: Download Operation

The JTAG mode is used to program the .sof file generated during project compilation into the FPGA. However, keep in mind that once the power is turned off and then back on, the code loaded via JTAG will be lost. This is because the FPGA does not retain the configuration after power loss. If the configuration chip itself is set to flash an LED, the light will continue to blink even after re-powering. To test whether the JTAG-downloaded data persists, you can first burn a non-flashing code into the configuration chip using JTAG, then perform the same download again to observe the result.

Dell latitude 3120,Dell 3120,Dell 3120 parts,Dell 3120 lcd,Dell 3120 keyboard,dell 3120 laptop

S-yuan Electronic Technology Limited , https://www.syuanelectronic.com